Nächste Seite: Re: 32 BitIch mache Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Re: Aufgaben und Übungen,

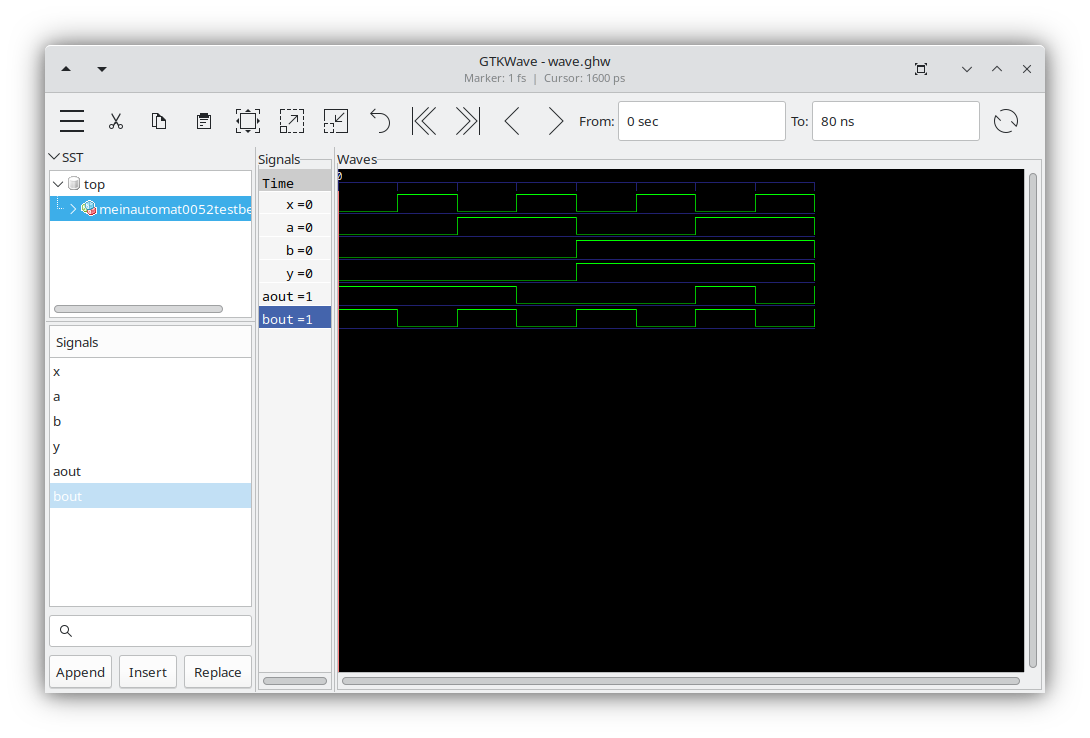

b a x b a y 0 0 0 0 1 1 0 1 0 0 1 0 1 0 2 0 1 0 1 1 0 3 0 1 1 0 0 0 4 1 0 0 1 0 1 5 1 0 1 0 0 1 6 1 1 0 1 1 1 7 1 1 1 0 0 1 b a x b 0 0 0 0 1 1 0 0 1 0 2 0 1 0 1 3 0 1 1 0 4 1 0 0 1 5 1 0 1 0 6 1 1 0 1 7 1 1 1 0 b a x a 0 0 0 0 1 1 0 0 1 1 2 0 1 0 1 3 0 1 1 0 4 1 0 0 0 5 1 0 1 0 6 1 1 0 1 7 1 1 1 0 b a x y 0 0 0 0 0 1 0 0 1 0 2 0 1 0 0 3 0 1 1 0 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 1 b a x b 0 0 0 0 1 2 0 1 0 1 4 1 0 0 1 6 1 1 0 1 b a x a 0 0 0 0 1 1 0 0 1 1 2 0 1 0 1 6 1 1 0 1 b a x y 4 1 0 0 1 5 1 0 1 1 6 1 1 0 1 7 1 1 1 1 b a x b Gruppe 0: 0 0 0 0 1 Gruppe 1: 2 0 1 0 1 4 1 0 0 1 Gruppe 2: 6 1 1 0 1 0:2 0 - 0 0:4 - 0 0 2:6 - 1 0 4:6 1 - 0 0:2 0 - 0 4:6 1 - 0 0:4 - 0 0 2:6 - 1 0 0:2:4:6 - - 0 0:4:2:6 - - 0 0:2:4:6 - - 0 b <= (not x) b <= (not (x)) b a x a Gruppe 0: 0 0 0 0 1 Gruppe 1: 1 0 0 1 1 2 0 1 0 1 Gruppe 2: 6 1 1 0 1 0:1 0 0 - 0:2 0 - 0 2:6 - 1 0 0 1 2 6 0:1 * * 0:2 * * 2:6 * * 0 1 2 6 0:1 * * 2:6 * * a <= (not b and not a) or (a and not x); a <= not ( (b or a) and (not a or x) ); b a x y Gruppe 1: 4 1 0 0 1 Gruppe 2: 5 1 0 1 1 6 1 1 0 1 Gruppe 3: 7 1 1 1 1 4:5 1 0 - 4:6 1 - 0 5:7 1 - 1 6:7 1 1 - 4:5 1 0 - 6:7 1 1 - 4:6 1 - 0 5:7 1 - 1 4:5:6:7 1 - - 4:6:5:7 1 - - y <= b y <= not (not b) b <= (not x) a <= (not b and not a) or (a and not x); y <= b library ieee; use ieee.std_logic_1164.all; entity meinuebergangsschaltnetz0052 is port ( bout, aout: out std_logic; b, a, x: in std_logic ); end; architecture verhalten meinuebergangsschaltnetz0052 is begin bout <= (not x) aout <= (not b and not a) or (a and not x); end; library ieee; use ieee.std_logic_1164.all; entity meinausgangsschaltnetz0052 is port ( y: out std_logic; b, a, x: in std_logic ); end; architecture verhalten of meinausgangsschaltnetz0052 is begin y <= b end; library ieee; use ieee.std_logic_1164.all; entity meinautomat0052testbench is port ( bout, aout: out std_logic; y: out std_logic ); end; architecture verhalten meinautomat0052testbench is component meinuebergangsschaltnetz0052 port ( bout, aout: out std_logic; b, a, x: in std_logic ); end component; component meinausgangsschaltnetz0052 port ( y: out std_logic; b, a, x: in std_logic ); end component; signal b, a, x: std_logic; begin sn1: meinuebergangsschaltnetz0052 PORT MAP (b=>b, a=>a, x=>x, bout=>bout, aout=>aout); sn2: meinausgangsschaltnetz0052 PORT MAP (b=>b, a=>a, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; end; [code] [img] https://www.ituenix.de/nextcloud/data/dave/files/Documents/david4/2023-12-20/Screenshot_20231220_230341.png [/img] [code] b a x b a y 0 0 0 0 1 1 0 1 0 0 1 0 1 0 2 0 1 0 1 1 0 3 0 1 1 0 0 0 4 1 0 0 1 0 1 5 1 0 1 0 0 1 6 1 1 0 1 1 1 7 1 1 1 0 0 1

library ieee; use ieee.std_logic_1164.all; entity meinuebergangsschaltnetz0052 is port ( bout, aout: out std_logic; b, a, x: in std_logic ); end; architecture verhalten of meinuebergangsschaltnetz0052 is begin bout <= (not x); aout <= (not b and not a) or (a and not x); end; library ieee; use ieee.std_logic_1164.all; entity meinausgangsschaltnetz0052 is port ( y: out std_logic; b, a, x: in std_logic ); end; architecture verhalten of meinausgangsschaltnetz0052 is begin y <= b; end; library ieee; use ieee.std_logic_1164.all; entity meinautomat0052testbench is port ( bout, aout: out std_logic; y: out std_logic ); end; architecture verhalten of meinautomat0052testbench is component meinuebergangsschaltnetz0052 port ( bout, aout: out std_logic; b, a, x: in std_logic ); end component; component meinausgangsschaltnetz0052 port ( y: out std_logic; b, a, x: in std_logic ); end component; signal b, a, x: std_logic; begin sn1: meinuebergangsschaltnetz0052 PORT MAP (b=>b, a=>a, x=>x, bout=>bout, aout=>aout); sn2: meinausgangsschaltnetz0052 PORT MAP (b=>b, a=>a, x=>x, y=>y); x <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns; a <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; b <= '0' after 0 ns, '0' after 10 ns, '0' after 20 ns, '0' after 30 ns, '1' after 40 ns, '1' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns; end;

-- Ah geil, es hat funktioniert!!!

-- Es tut!!!

-- Ich probiere jetzt einen Ripple Carry Adder

library ieee;

use ieee.std_logic_1164.all;

entity meinschaltnetz is

port (

a, b: in std_logic;

y: out std_logic

);

end;

architecture verhalten of meinschaltnetz is

begin

y <= a and b;

end;

library ieee;

use ieee.std_logic_1164.all;

entity meingrosseschaltnetz is

port (

y: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture verhalten of meingrosseschaltnetz is

component meinschaltnetz

port (

a, b: in std_logic;

y: out std_logic

);

end component;

begin

l1:

for i in 0 to 31 generate

sn: meinschaltnetz PORT MAP (b=>b(i), a=>a(i), y=>y(i));

end generate;

end;

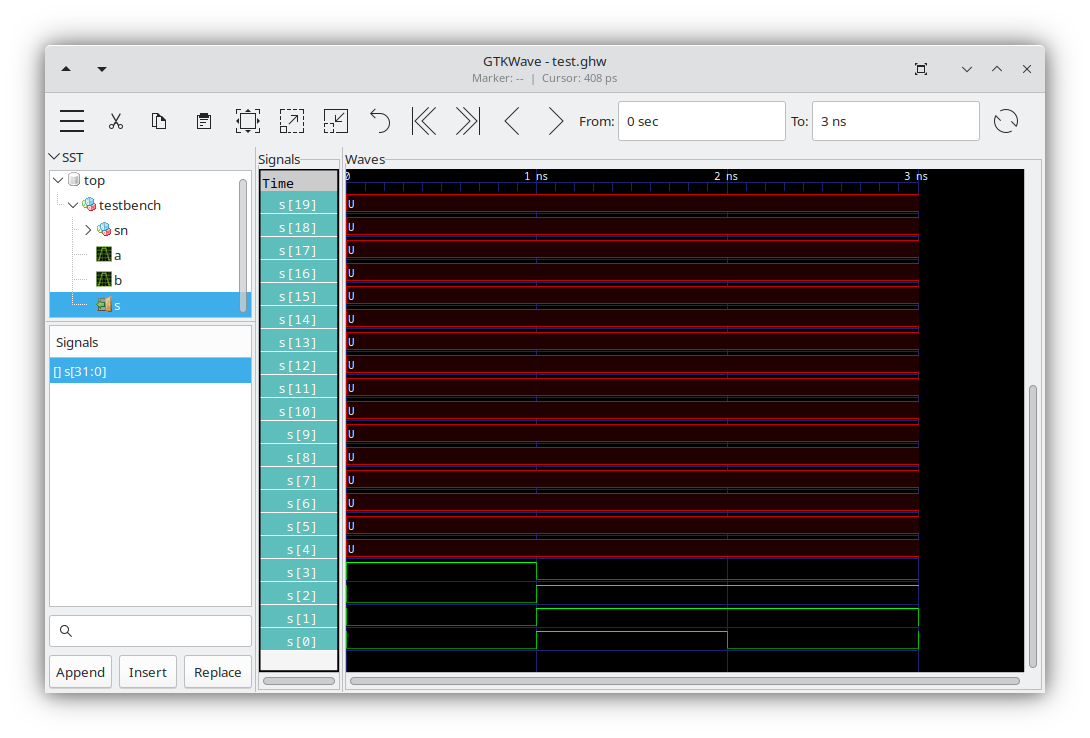

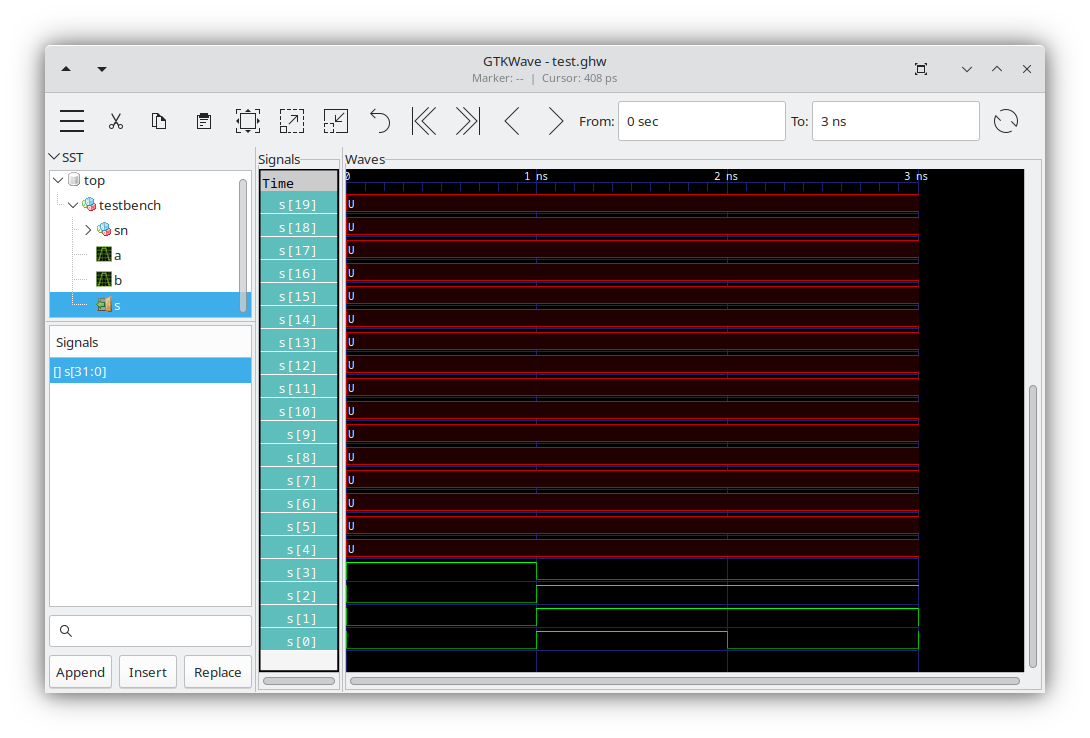

-- Scheint mit dem Ripple Carry Adder zu funktionierern

library ieee;

use ieee.std_logic_1164.all;

entity fulladder is

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end;

architecture verhalten of fulladder is

begin

s <= a xor b xor c;

u <= (a and b) or ((a or b) and c);

end;

library ieee;

use ieee.std_logic_1164.all;

entity ripplecarryadder is

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end;

architecture verhalten of ripplecarryadder is

component fulladder

port (

a, b, c: in std_logic;

s, u: out std_logic

);

end component;

signal c : std_logic_vector (31 downto 0);

signal u : std_logic_vector (31 downto 0);

begin

c(0) <= '0';

add1: fulladder PORT MAP (c=>c(0),b=>b(0),a=>a(0),s=>s(0),u=>u(0));

l1:

for i in 1 to 31 generate

sn: fulladder PORT MAP (c=>u(i-1),b=>b(i),a=>a(i),s=>s(i),u=>u(i));

end generate;

end;

library ieee;

use ieee.std_logic_1164.all;

entity testbench is

port (

s: out std_logic_vector (31 downto 0)

);

end;

architecture verhalten of testbench is

component ripplecarryadder

port (

s: out std_logic_vector (31 downto 0);

b, a: in std_logic_vector (31 downto 0)

);

end component;

signal b, a: std_logic_vector (31 downto 0);

begin

sn: ripplecarryadder PORT MAP (b=>b, a=>a, s=>s);

a (0) <= '1' after 0 ns, '0' after 1 ns , '1' after 2 ns, '0' after 3 ns;

b (0) <= '1' after 0 ns;

a (1) <= '1' after 0 ns, '0' after 2 ns;

b (1) <= '0' after 0 ns;

a (2) <= '0' after 0 ns;

b (2) <= '1' after 0 ns;

a (3) <= '1' after 0 ns;

b (3) <= '1' after 0 ns;

end;

a (0) <= '1' after 0 ns, '0' after 1 ns , '1' after 2 ns, '0' after 3 ns;

b (0) <= '1' after 0 ns;

a (1) <= '1' after 0 ns, '0' after 2 ns;

b (1) <= '0' after 0 ns;

a (2) <= '0' after 0 ns;

b (2) <= '1' after 0 ns;

a (3) <= '1' after 0 ns;

b (3) <= '1' after 0 ns;

-- wenn man das anguckt und das bild, dann scheint das gut zu funktionieren