Nächste Seite: Re: Aufgaben und Übungen, Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: TTL-Schaltnetz in DNFTTL-Schaltnetz in

z0+ = z0 AND NOT Knopf OR z2 z1+ = z0 AND Knopf z2+ = z1 Farbe = z0 AND Knopf OR z1 OR z2

Wie kommt es dazu? Zunächst, was wir sehen, dieses Übergangsschaltnetz aber auch das Ausgangsschaltnetz ist minimiert worden. Ich kenne diese Formeln auswendig. Und halte auch die Regeln für die Ampel für würdig auswendig gelernt zu werden. Normalerweise wird es nicht bei drei Sekunden bleiben. Was ist zu tun, wenn wir eine Feste Taktdauer haben? Dann führen wir einen weiteren Zustand ein

z0+ = z0 AND NOT Knopf OR z3 z1+ = z0 AND Knopf z2+ = z1 z3+ = z2 Farbe = z0 AND Knopf OR z1 OR z2

Z0, Z1, Z2, Z3

So, jeder Zustand muss ein Mal irgendwie erreicht werden. Es muss nicht jede Eingabe bedient werden. Das sind die Bedingungen für das Übungsprogramm

david@laptop-peaq:~\$ ./a.out Zustand Eingabe Ausgabe Folgezustand 0 00 0 3 0 01 0 2 0 11 0 2 1 00 1 0 1 01 1 1 1 10 0 1 1 11 1 1 2 00 0 2 2 01 0 3 2 10 0 0 2 11 0 3 3 00 1 1 david@laptop-peaq:~\$

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int x0line, x1line, x2line, x3line;

int nfollowed;

int z0reached, z1reached, z2reached, z3reached;

int i, j;

int z [4][4];

int k, l;

int v;

int nf;

srand ((unsigned)time (\&t));

z0reached = 0;

z1reached = 0;

z2reached = 0;

z3reached = 0;

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = EMPTY_Z;

}

nfollowed = 0;

for (i = 0; i < 4; i++) {

x0line = rand () % 2;

x1line = rand () % 2;

x2line = rand () % 2;

x3line = rand () % 2;

nfollowed += x0line + x1line + x2line + x3line;

if (x0line == 1)

z [i][0] = UNINIT_Z;

if (x1line == 1)

z [i][1] = UNINIT_Z;

if (x2line == 1)

z [i][2] = UNINIT_Z;

if (x3line == 1)

z [i][3] = UNINIT_Z;

if ((x0line + x1line + x2line + x3line) == 0) {

z [i][0] = UNINIT_Z;

nfollowed += 1;

}

}

z0reached = 0;

z1reached = 0;

z2reached = 0;

z3reached = 0;

nf = nfollowed;

for (i = 0, k = 0, l = 0; i < nf; i++) {

v = rand () % 4;

if (v == 0)

z0reached = 1;

if (v == 1)

z1reached = 1;

if (v == 2)

z2reached = 1;

if (v == 3)

z3reached = 1;

while ((k < 4) \&\& (l < 4) \&\& (z [k][l] != UNINIT_Z)) {

while ((l < 4) \&\& (z [k][l] != UNINIT_Z))

l++;

if (z [k][l] != UNINIT_Z) {

l = 0;

k++;

}

}

nfollowed--;

if (nfollowed == (z0reached + z1reached + z2reached + z3reached)) {

if (z0reached == 0) {

v = 0;

z0reached = 1;

}

else if (z1reached == 0) {

v = 1;

z1reached = 1;

}

else if (z2reached == 0) {

v = 2;

z2reached = 1;

}

else if (z3reached == 0) {

v = 3;

z3reached = 1;

}

}

z [k][l] = v;

k += (l/4);

l = (l+1) % 4;

}

printf ("ZustandtEingabetAusgabetFolgezustandn");

for (i = 0; i < 4; i++) {

if (z [i][0] != EMPTY_Z)

printf ("%itt00tt%itt%in", i, rand () % 2, z [i][0]);

if (z [i][1] != EMPTY_Z)

printf ("%itt01tt%itt%in", i, rand () % 2, z [i][1]);

if (z [i][2] != EMPTY_Z)

printf ("%itt10tt%itt%in", i, rand () % 2, z [i][2]);

if (z [i][3] != EMPTY_Z)

printf ("%itt11tt%itt%in", i, rand () % 2, z [i][3]);

}

return 0;

}

So, zu dieser Übung mache ich den Automaten

Zustand Eingabe Ausgabe Folgezustand 0 10 1 3 1 10 0 2 2 10 1 1 2 11 1 0 3 00 1 1 3 01 0 1 3 11 0 1

wie wir sehen, ist noch ein Fehler im Programm drin

Zustand Eingabe Ausgabe Folgezustand

0 00 0 0

0 01 1 0

0 10 1 0

1 00 0 0

1 01 0 0

1 11 1 1

2 00 1 2

2 11 1 3

3 11 0 1

Zustand Eingabe Ausgabe Folgezustand

0 10 1 3

1 10 0 2

2 10 1 1

2 11 1 0

3 00 1 1

3 01 0 1

3 11 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand

z3+ z2+ z1+ z0+

0 10 1 3 1 0 0 0

1 10 0 2 0 1 0 0

2 10 1 1 0 0 1 0

2 11 1 0 0 0 0 1

3 00 1 1 0 0 1 0

3 01 0 1 0 0 1 0

3 11 0 1 0 0 1 0

was ist mit den übrigen Eingaben?

Also, meine einfachste Idee, wäre ein Mal in die eine Richtung zu sortieren, mal in die andere. Reihenweise

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Im nächsten Schritt Spaltenweise. Dann wieder Zeilweise und so weiter. So lange wie man lustig ist.

david@laptop-peaq:~\$ ./a.out 3 0 0 0 0 1 2 3 0 1 2 3 3 0 0 0 david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 1 2 3 3 2 1 0 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 1 0 3 2 1 0 0 1 2 3 3 2 1 0 david@laptop-peaq:~\$ ./a.out 0 1 2 3 3 2 1 0 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 1 0 0 1 2 3 3 2 1 0 0 1 2 3 david@laptop-peaq:~\$ ./a.out 3 2 1 0 3 2 1 0 3 2 1 0 0 1 2 3 david@laptop-peaq:~\$

david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 2 2 3 3 1 2 0 0 1 2 3 0 1 1 3 david@laptop-peaq:~\$ ./a.out 0 1 2 3 0 1 2 3 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 2 3 0 1 2 3 0 1 1 0 3 2 1 0 david@laptop-peaq:~\$

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Jetzt machen wir das randomized oft

Ich habe jetzt folgendes hingekriegt

david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 3 3 0 1 2 2 1 2 1 1 3 2 0 0 3 david@laptop-peaq:~\$ ./a.out 0 3 3 0 1 2 2 1 2 1 1 3 2 0 0 3 david@laptop-peaq:~\$ ./a.out 3 0 3 3 3 1 2 2 1 2 1 0 0 2 1 0 david@laptop-peaq:~\$ ./a.out 3 1 3 3 0 1 2 3 0 1 2 2 0 2 1 0 david@laptop-peaq:~\$ ./a.out 3 1 3 3 0 1 2 3 0 1 2 2 0 2 1 0 david@laptop-peaq:~\$ ./a.out 0 0 0 0 2 2 1 1 3 2 1 1 3 3 2 3 david@laptop-peaq:~\$ ./a.out 0 0 1 0 0 1 1 2 1 2 2 3 2 3 3 3 david@laptop-peaq:~\$

Mit dem Code

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

int n;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (n = rand () % 100; n >= 0; n--) {

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] < z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] < z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Ich habe jetzt für den Fall, dass bei der Sortierung

jenachdem ein Mal so rum sortiert ein Mal so rum\\

\\

Dass jetzt in einer Zeile 0,0,0,0 stehen lasse ich mal aus Gnade zum Algorithmus, so stehen.\\

\\

Also, so sieht das Programm jetzt aus, Ausgabe\\

\begin{verbatim}

david@laptop-peaq:~\$ ./a.out

0 0 0 0

3 1 1 1

3 2 2 1

3 2 2 3

Zustand Eingabe Ausgabe Folgezustand

0 0 0 0

0 1 1 0

0 2 2 0

0 3 2 0

1 0 3 3

1 1 3 1

1 2 1 1

1 3 1 1

2 0 3 3

2 1 1 2

2 2 2 2

2 3 0 1

3 0 1 3

3 1 1 2

3 2 2 2

3 3 2 3

david@laptop-peaq:~\$

Ich habe mir mal erlaubt, die Ausgabe

>y1y0Und die Eingabe

>x1x0

nicht binär zu kodieren. Hier das Programm

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

int n;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (n = rand () % 100; n >= 0; n--) {

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] < z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] < z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

printf ("ZustandtEingabetAusgabetFolgezustandn");

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%itt%itt%itt%in", i, j, rand () % 4, z[i][j]);

}

return 0;

}

Diese Aufgabe mache ich jetzt

2 3 0 3 2 2 1 3 0 1 2 1 0 0 3 1 Zustand Eingabe Ausgabe Folgezustand 0 0 2 2 0 1 1 3 0 2 0 0 0 3 3 3 1 0 3 2 1 1 3 2 1 2 0 1 1 3 1 3 2 0 2 0 2 1 1 1 2 2 1 2 2 3 3 1 3 0 3 0 3 1 1 0 3 2 1 3 3 3 0 1

So, ergibt das mit den Kodierungen einen gewissen sinn

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

Jetzt mache ich dazu das Schaltwerk und das nachher auch in VHDL.

Da kann man trotz allem ein Quine Mc Cluskey draus machen, ich zeige es gleich

Nein, kann man nicht, aber was ähnliches. Es geht nicht, weil die Zustände unär kodiert sind, deswegen nicht

Aber, man kann es geschickter hinschreiben

so ist das schon besser

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

++++++++++++++++++++++++++

Zustand z3+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 1 1 3 1 0 0 0 0 1 0 1

0 3 3 3 1 0 0 0 1 1 1 1

1 3 1 3 1 0 0 0 1 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

z3+ <= (z0 and not x1 and x0) or (z0 and x1 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

Zustand z2+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 2 1 2 0 1 0 0 1 0 0 1

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0) or (z2 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

Zustand z1+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

1 2 0 1 0 0 1 0 1 0 0 0

2 1 1 1 0 0 1 0 0 1 0 1

2 3 3 1 0 0 1 0 1 1 1 1

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

Zustand z0+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 0 0 0 0 0 1 1 0 0 0

2 0 2 0 0 0 0 1 0 0 1 0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 3 0 1 0 0 0 1 1 1 0 0

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

Ausgabe y1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 0 2 0 0 0 0 1 0 0 1 0

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

Ausgabe y0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 1 0 1

0 2 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 1 3 1 0 0 0 1 1 0 1

2 0 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0) z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0) z1+ <= (z1 and x1 and not x0) or (z2 and x0) z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0) y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0) y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

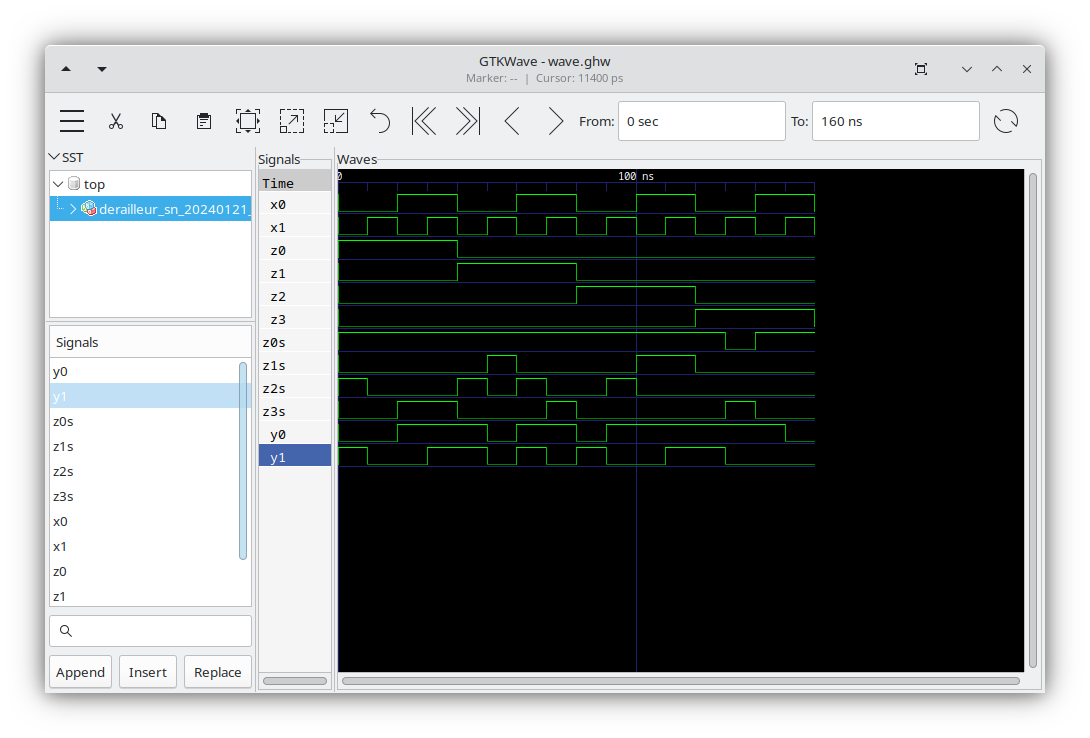

Jetzt mache ich dazu gewohnheitsmässig einen VHDL Code von mir aus implementiere ich die Speicherglieder - ich mache das Schaltwerk dazu. Mit Caneda. Gezeichnet.

Nein, ich muss noch lernen. Ich mache ein normales Schaltnetz in VHDL dazu und das ist alles. Ich drücke es in VHDL aus, ohne Speicherglieder. Wir wissen ja

Q <= R NOR Q' Q' <= S NOR Q

Das müsste für das RS-Latch schon reichen. Jetzt Code, dann muss ich weiter lernen

Übrigens, lässt sich das in VHDL ohne FF's so oder so einfacher testen. Sonst müsste ich die alle setzen. Einfacher ist es, ich benutze sie nicht, dann kann ich in der Testbench sehen, ob das Schaltnetz richtig ist, und in gtkwave angucken

So sieht der neue "Testbenchgeneratoräus hoffentlich richtig

#include <stdio.h>

int main (void) {

int i;

int j;

int k, l;

int v = 0;

char *a [] = {"x1", "x0"};

int q;

printf ("z0 <= '1' after 0 ns, '0' after 40 ns;n");

printf ("z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;n");

printf ("z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;n");

printf ("z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;n");

for (k = 0, l = 1; k < 2; k++, l = l*2) {

printf ("%s <= ", a [k]);

for (j = 1, i = 0, v = 0; i < 160; i+=10, j++) {

printf ("'%i' after %i ns, ", v, i);

if ((j % l) == 0) {

v = (v + 1) % 2;

}

}

j = j%2;

printf ("'%i' after %i ns;nn", v, i);

}

return 0;

}

und so der VHDL Code bisher

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic;

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic;

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic;

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y2=>2);

Ich hänge das jetzt an, gucke, wo Fehler sind, und hoffe, es kommt das Ergebnis raus, wie in der Zustandstabelle

So, wäre der VHDL Code ohne Syntax Fehler

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) or (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y0=>y0);

z0 <= '1' after 0 ns, '0' after 40 ns;

z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;

z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;

z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;

x1 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns;

x0 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns, '0' after 160 ns;

end;

Ich poste das Ergebnis von

gtkwave

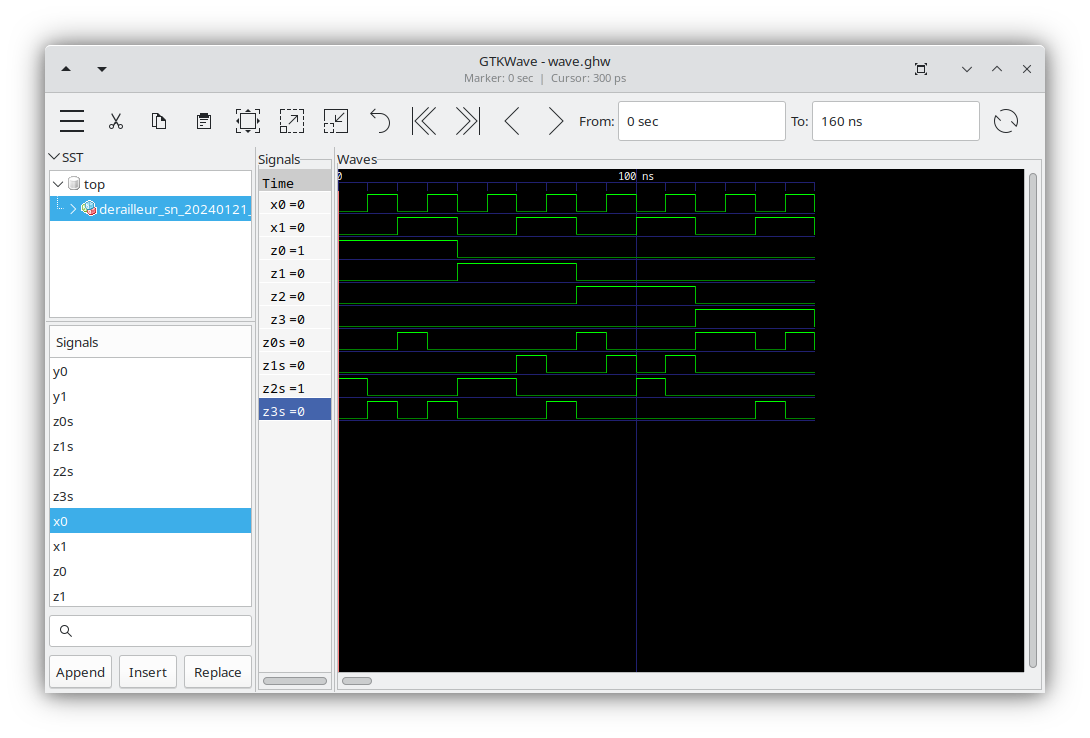

Scheint ein kleiner Fehler, bei einem Zustand drin zu sein, den Rest muss ich mir angucken, aber die Eingangssignale wurden richtig generiert.

So, ich habe es - die Ausgabe habe ich jetzt nicht angeguckt, aber es lag daran, dass ich die Gleichung ohne Quine Mc Cluskey oder KV Diagramm verkürzt habe - das hatte Auswirkungen auf alle Zustände - bei Unär Codiert auf alle Zustände, wenn einer falsch ist. Jetzt stimmt es.

Die Ausgabe habe ich nicht kontrolliert

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

++++++++++++++++++++++++++

Zustand z3+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 1 1 3 1 0 0 0 0 1 0 1

0 3 3 3 1 0 0 0 1 1 1 1

1 3 1 3 1 0 0 0 1 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

z3+ <= (z0 and not x1 and x0) or (z0 and x1 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

Zustand z2+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 2 1 2 0 1 0 0 1 0 0 1

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0) or (z2 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

Zustand z1+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

1 2 0 1 0 0 1 0 1 0 0 0

2 1 1 1 0 0 1 0 0 1 0 1

2 3 3 1 0 0 1 0 1 1 1 1

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

Zustand z0+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 0 0 0 0 0 1 1 0 0 0

2 0 2 0 0 0 0 1 0 0 1 0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 3 0 1 0 0 0 1 1 1 0 0

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or (z3 and not x1 and not x0) or (z3 and not x1 and x0) or (z3 and x1 and x0)

Ausgabe y1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 0 2 0 0 0 0 1 0 0 1 0

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

Ausgabe y0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 1 0 1

0 2 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 1 3 1 0 0 0 1 1 0 1

2 0 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or (z3 and not x1 and not x0) or (z3 and not x1 and x0) or (z3 and x1 and x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) or (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y0=>y0);

z0 <= '1' after 0 ns, '0' after 40 ns;

z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;

z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;

z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns, '0' after 160 ns;

end;

Bzw. hier hat es keine Auswirkungen, weil es Eingangs und Ausgangsvariablen im Übergangsschaltnetz gäbe

zw, zw+

z0+ = z0 AND NOT Knopf OR z2 z1+ = z0 AND Knopf z2+ = z1 Farbe = z0 AND Knopf OR z1 OR z2

Wie kommt es dazu? Zunächst, was wir sehen, dieses Übergangsschaltnetz aber auch das Ausgangsschaltnetz ist minimiert worden. Ich kenne diese Formeln auswendig. Und halte auch die Regeln für die Ampel für würdig auswendig gelernt zu werden. Normalerweise wird es nicht bei drei Sekunden bleiben. Was ist zu tun, wenn wir eine Feste Taktdauer haben? Dann führen wir einen weiteren Zustand ein

z0+ = z0 AND NOT Knopf OR z3 z1+ = z0 AND Knopf z2+ = z1 z3+ = z2 Farbe = z0 AND Knopf OR z1 OR z2

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand z0+ z1+ z2+

Sondern hier muss ich schon überlegen, wie ich das mache. Wahrscheinlich so

Zustand Eingabe Ausgabe Folgezustand

Ich habe immer eine Eingabe

x0, x1

Weil mit einer einzigen, wird es langweilig. Und vier Zustände

Z0, Z1, Z2, Z3

So, jeder Zustand muss ein Mal irgendwie erreicht werden. Es muss nicht jede Eingabe bedient werden. Das sind die Bedingungen für das Übungsprogramm

david@laptop-peaq:~\$ ./a.out Zustand Eingabe Ausgabe Folgezustand 0 00 0 3 0 01 0 2 0 11 0 2 1 00 1 0 1 01 1 1 1 10 0 1 1 11 1 1 2 00 0 2 2 01 0 3 2 10 0 0 2 11 0 3 3 00 1 1 david@laptop-peaq:~\$

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int x0line, x1line, x2line, x3line;

int nfollowed;

int z0reached, z1reached, z2reached, z3reached;

int i, j;

int z [4][4];

int k, l;

int v;

int nf;

srand ((unsigned)time (\&t));

z0reached = 0;

z1reached = 0;

z2reached = 0;

z3reached = 0;

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = EMPTY_Z;

}

nfollowed = 0;

for (i = 0; i < 4; i++) {

x0line = rand () % 2;

x1line = rand () % 2;

x2line = rand () % 2;

x3line = rand () % 2;

nfollowed += x0line + x1line + x2line + x3line;

if (x0line == 1)

z [i][0] = UNINIT_Z;

if (x1line == 1)

z [i][1] = UNINIT_Z;

if (x2line == 1)

z [i][2] = UNINIT_Z;

if (x3line == 1)

z [i][3] = UNINIT_Z;

if ((x0line + x1line + x2line + x3line) == 0) {

z [i][0] = UNINIT_Z;

nfollowed += 1;

}

}

z0reached = 0;

z1reached = 0;

z2reached = 0;

z3reached = 0;

nf = nfollowed;

for (i = 0, k = 0, l = 0; i < nf; i++) {

v = rand () % 4;

if (v == 0)

z0reached = 1;

if (v == 1)

z1reached = 1;

if (v == 2)

z2reached = 1;

if (v == 3)

z3reached = 1;

while ((k < 4) \&\& (l < 4) \&\& (z [k][l] != UNINIT_Z)) {

while ((l < 4) \&\& (z [k][l] != UNINIT_Z))

l++;

if (z [k][l] != UNINIT_Z) {

l = 0;

k++;

}

}

nfollowed--;

if (nfollowed == (z0reached + z1reached + z2reached + z3reached)) {

if (z0reached == 0) {

v = 0;

z0reached = 1;

}

else if (z1reached == 0) {

v = 1;

z1reached = 1;

}

else if (z2reached == 0) {

v = 2;

z2reached = 1;

}

else if (z3reached == 0) {

v = 3;

z3reached = 1;

}

}

z [k][l] = v;

k += (l/4);

l = (l+1) % 4;

}

printf ("ZustandtEingabetAusgabetFolgezustandn");

for (i = 0; i < 4; i++) {

if (z [i][0] != EMPTY_Z)

printf ("%itt00tt%itt%in", i, rand () % 2, z [i][0]);

if (z [i][1] != EMPTY_Z)

printf ("%itt01tt%itt%in", i, rand () % 2, z [i][1]);

if (z [i][2] != EMPTY_Z)

printf ("%itt10tt%itt%in", i, rand () % 2, z [i][2]);

if (z [i][3] != EMPTY_Z)

printf ("%itt11tt%itt%in", i, rand () % 2, z [i][3]);

}

return 0;

}

So, zu dieser Übung mache ich den Automaten

Zustand Eingabe Ausgabe Folgezustand 0 10 1 3 1 10 0 2 2 10 1 1 2 11 1 0 3 00 1 1 3 01 0 1 3 11 0 1

wie wir sehen, ist noch ein Fehler im Programm drin

Zustand Eingabe Ausgabe Folgezustand

0 00 0 0

0 01 1 0

0 10 1 0

1 00 0 0

1 01 0 0

1 11 1 1

2 00 1 2

2 11 1 3

3 11 0 1

Zustand Eingabe Ausgabe Folgezustand

0 10 1 3

1 10 0 2

2 10 1 1

2 11 1 0

3 00 1 1

3 01 0 1

3 11 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand

z3+ z2+ z1+ z0+

0 10 1 3 1 0 0 0

1 10 0 2 0 1 0 0

2 10 1 1 0 0 1 0

2 11 1 0 0 0 0 1

3 00 1 1 0 0 1 0

3 01 0 1 0 0 1 0

3 11 0 1 0 0 1 0

was ist mit den übrigen Eingaben?

Also, meine einfachste Idee, wäre ein Mal in die eine Richtung zu sortieren, mal in die andere. Reihenweise

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Im nächsten Schritt Spaltenweise. Dann wieder Zeilweise und so weiter. So lange wie man lustig ist.

david@laptop-peaq:~\$ ./a.out 3 0 0 0 0 1 2 3 0 1 2 3 3 0 0 0 david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 1 2 3 3 2 1 0 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 1 0 3 2 1 0 0 1 2 3 3 2 1 0 david@laptop-peaq:~\$ ./a.out 0 1 2 3 3 2 1 0 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 1 0 0 1 2 3 3 2 1 0 0 1 2 3 david@laptop-peaq:~\$ ./a.out 3 2 1 0 3 2 1 0 3 2 1 0 0 1 2 3 david@laptop-peaq:~\$

david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 2 2 3 3 1 2 0 0 1 2 3 0 1 1 3 david@laptop-peaq:~\$ ./a.out 0 1 2 3 0 1 2 3 3 2 1 0 3 2 1 0 david@laptop-peaq:~\$ ./a.out 3 2 2 3 0 1 2 3 0 1 1 0 3 2 1 0 david@laptop-peaq:~\$

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Jetzt machen wir das randomized oft

Ich habe jetzt folgendes hingekriegt

david@laptop-peaq:~\$ gcc automat5.c david@laptop-peaq:~\$ ./a.out 0 3 3 0 1 2 2 1 2 1 1 3 2 0 0 3 david@laptop-peaq:~\$ ./a.out 0 3 3 0 1 2 2 1 2 1 1 3 2 0 0 3 david@laptop-peaq:~\$ ./a.out 3 0 3 3 3 1 2 2 1 2 1 0 0 2 1 0 david@laptop-peaq:~\$ ./a.out 3 1 3 3 0 1 2 3 0 1 2 2 0 2 1 0 david@laptop-peaq:~\$ ./a.out 3 1 3 3 0 1 2 3 0 1 2 2 0 2 1 0 david@laptop-peaq:~\$ ./a.out 0 0 0 0 2 2 1 1 3 2 1 1 3 3 2 3 david@laptop-peaq:~\$ ./a.out 0 0 1 0 0 1 1 2 1 2 2 3 2 3 3 3 david@laptop-peaq:~\$

Mit dem Code

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

int n;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (n = rand () % 100; n >= 0; n--) {

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] < z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] < z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

return 0;

}

Ich habe jetzt für den Fall, dass bei der Sortierung

jenachdem ein Mal so rum sortiert ein Mal so rum\\

\\

Dass jetzt in einer Zeile 0,0,0,0 stehen lasse ich mal aus Gnade zum Algorithmus, so stehen.\\

\\

Also, so sieht das Programm jetzt aus, Ausgabe\\

\begin{verbatim}

david@laptop-peaq:~\$ ./a.out

0 0 0 0

3 1 1 1

3 2 2 1

3 2 2 3

Zustand Eingabe Ausgabe Folgezustand

0 0 0 0

0 1 1 0

0 2 2 0

0 3 2 0

1 0 3 3

1 1 3 1

1 2 1 1

1 3 1 1

2 0 3 3

2 1 1 2

2 2 2 2

2 3 0 1

3 0 1 3

3 1 1 2

3 2 2 2

3 3 2 3

david@laptop-peaq:~\$

Ich habe mir mal erlaubt, die Ausgabe

>y1y0Und die Eingabe

>x1x0

nicht binär zu kodieren. Hier das Programm

#include <stdio.h>

#include <stdlib.h>

#include <time.h>

#define EMPTY_Z -1

#define UNINIT_Z -2

int main (void) {

time_t t;

int i, j;

int z [4][4];

int v;

int k, l;

int n;

srand ((unsigned)time (\&t));

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

z [i][j] = j;

}

for (n = rand () % 100; n >= 0; n--) {

for (i = 0; i < 4; i++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] > z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[i][l] < z[i][k]) {

t = z [i][l];

z [i][l] = z[i][k];

z [i][k] = t;

}

}

}

}

}

for (j = 0; j < 4; j++) {

if ((rand () % 2) == 0) {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] > z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

else {

for (k = 0; k < 4; k++) {

for (l = k + 1; l < 4; l++) {

if (z[l][j] < z[k][j]) {

t = z [l][j];

z [l][j] = z[k][j];

z [k][j] = t;

}

}

}

}

}

}

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%i ", z[i][j]);

printf ("n");

}

printf ("ZustandtEingabetAusgabetFolgezustandn");

for (i = 0; i < 4; i++) {

for (j = 0; j < 4; j++)

printf ("%itt%itt%itt%in", i, j, rand () % 4, z[i][j]);

}

return 0;

}

Diese Aufgabe mache ich jetzt

2 3 0 3 2 2 1 3 0 1 2 1 0 0 3 1 Zustand Eingabe Ausgabe Folgezustand 0 0 2 2 0 1 1 3 0 2 0 0 0 3 3 3 1 0 3 2 1 1 3 2 1 2 0 1 1 3 1 3 2 0 2 0 2 1 1 1 2 2 1 2 2 3 3 1 3 0 3 0 3 1 1 0 3 2 1 3 3 3 0 1

So, ergibt das mit den Kodierungen einen gewissen sinn

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

Jetzt mache ich dazu das Schaltwerk und das nachher auch in VHDL.

Da kann man trotz allem ein Quine Mc Cluskey draus machen, ich zeige es gleich

Nein, kann man nicht, aber was ähnliches. Es geht nicht, weil die Zustände unär kodiert sind, deswegen nicht

Aber, man kann es geschickter hinschreiben

so ist das schon besser

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

++++++++++++++++++++++++++

Zustand z3+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 1 1 3 1 0 0 0 0 1 0 1

0 3 3 3 1 0 0 0 1 1 1 1

1 3 1 3 1 0 0 0 1 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

z3+ <= (z0 and not x1 and x0) or (z0 and x1 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

Zustand z2+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 2 1 2 0 1 0 0 1 0 0 1

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0) or (z2 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

Zustand z1+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

1 2 0 1 0 0 1 0 1 0 0 0

2 1 1 1 0 0 1 0 0 1 0 1

2 3 3 1 0 0 1 0 1 1 1 1

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

Zustand z0+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 0 0 0 0 0 1 1 0 0 0

2 0 2 0 0 0 0 1 0 0 1 0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 3 0 1 0 0 0 1 1 1 0 0

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

Ausgabe y1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 0 2 0 0 0 0 1 0 0 1 0

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

Ausgabe y0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 1 0 1

0 2 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 1 3 1 0 0 0 1 1 0 1

2 0 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0) z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0) z1+ <= (z1 and x1 and not x0) or (z2 and x0) z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0) y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0) y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

Jetzt mache ich dazu gewohnheitsmässig einen VHDL Code von mir aus implementiere ich die Speicherglieder - ich mache das Schaltwerk dazu. Mit Caneda. Gezeichnet.

Nein, ich muss noch lernen. Ich mache ein normales Schaltnetz in VHDL dazu und das ist alles. Ich drücke es in VHDL aus, ohne Speicherglieder. Wir wissen ja

Q <= R NOR Q' Q' <= S NOR Q

Das müsste für das RS-Latch schon reichen. Jetzt Code, dann muss ich weiter lernen

Übrigens, lässt sich das in VHDL ohne FF's so oder so einfacher testen. Sonst müsste ich die alle setzen. Einfacher ist es, ich benutze sie nicht, dann kann ich in der Testbench sehen, ob das Schaltnetz richtig ist, und in gtkwave angucken

So sieht der neue "Testbenchgeneratoräus hoffentlich richtig

#include <stdio.h>

int main (void) {

int i;

int j;

int k, l;

int v = 0;

char *a [] = {"x1", "x0"};

int q;

printf ("z0 <= '1' after 0 ns, '0' after 40 ns;n");

printf ("z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;n");

printf ("z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;n");

printf ("z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;n");

for (k = 0, l = 1; k < 2; k++, l = l*2) {

printf ("%s <= ", a [k]);

for (j = 1, i = 0, v = 0; i < 160; i+=10, j++) {

printf ("'%i' after %i ns, ", v, i);

if ((j % l) == 0) {

v = (v + 1) % 2;

}

}

j = j%2;

printf ("'%i' after %i ns;nn", v, i);

}

return 0;

}

und so der VHDL Code bisher

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic;

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic;

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic;

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y2=>2);

Ich hänge das jetzt an, gucke, wo Fehler sind, und hoffe, es kommt das Ergebnis raus, wie in der Zustandstabelle

So, wäre der VHDL Code ohne Syntax Fehler

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) or (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y0=>y0);

z0 <= '1' after 0 ns, '0' after 40 ns;

z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;

z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;

z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;

x1 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns;

x0 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns, '0' after 160 ns;

end;

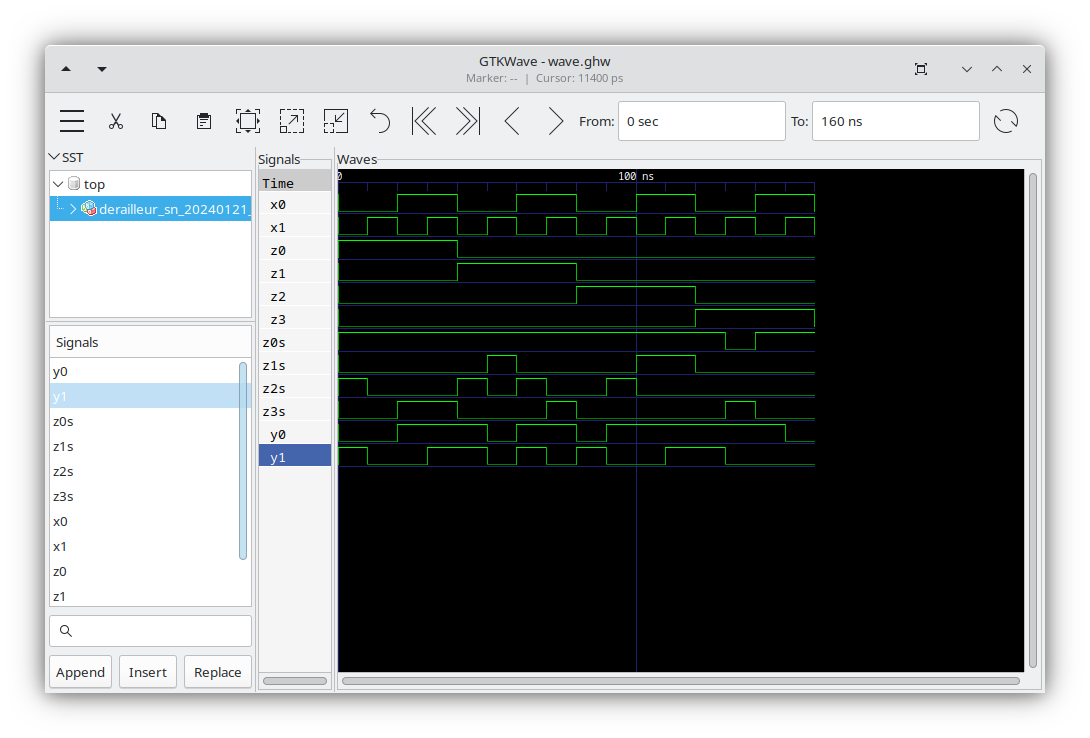

Ich poste das Ergebnis von

gtkwave

Scheint ein kleiner Fehler, bei einem Zustand drin zu sein, den Rest muss ich mir angucken, aber die Eingangssignale wurden richtig generiert.

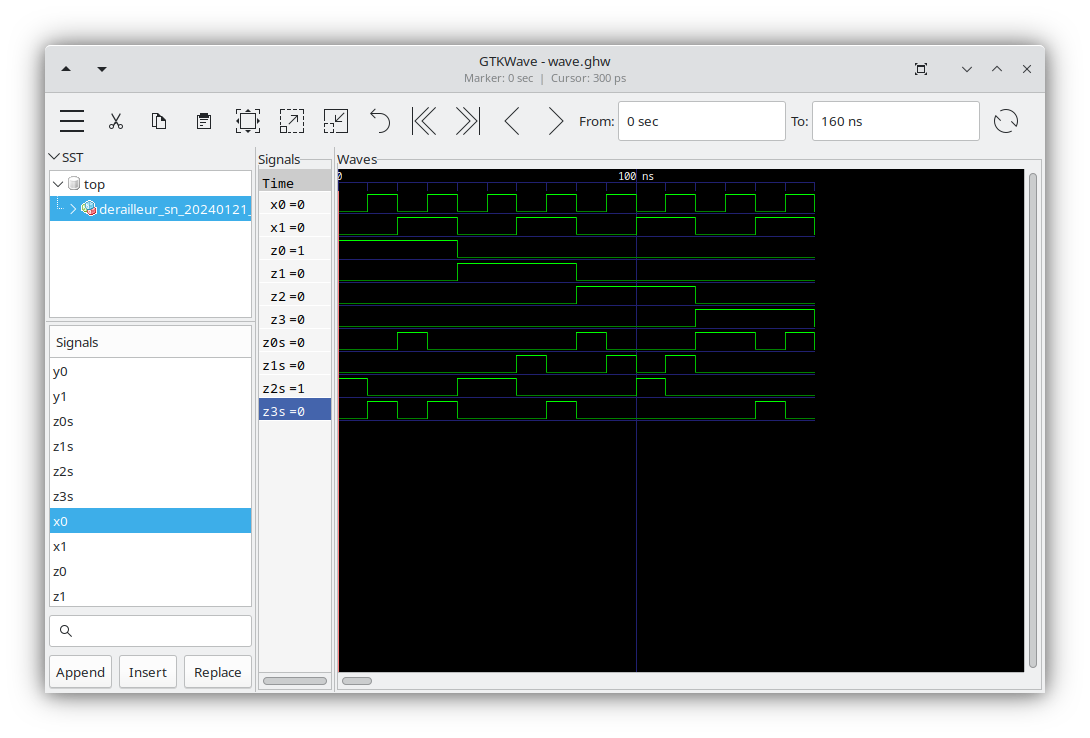

So, ich habe es - die Ausgabe habe ich jetzt nicht angeguckt, aber es lag daran, dass ich die Gleichung ohne Quine Mc Cluskey oder KV Diagramm verkürzt habe - das hatte Auswirkungen auf alle Zustände - bei Unär Codiert auf alle Zustände, wenn einer falsch ist. Jetzt stimmt es.

Die Ausgabe habe ich nicht kontrolliert

2 3 0 3

2 2 1 3

0 1 2 1

0 0 3 1

Zustand Eingabe Ausgabe Folgezustand

0 0 2 2

0 1 1 3

0 2 0 0

0 3 3 3

1 0 3 2

1 1 3 2

1 2 0 1

1 3 1 3

2 0 2 0

2 1 1 1

2 2 1 2

2 3 3 1

3 0 3 0

3 1 1 0

3 2 1 3

3 3 0 1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 1 1 3 1 0 0 0 0 1 0 1

0 2 0 0 0 0 0 1 1 0 0 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 0 1 0 0 1 0 1 0 0 0

1 3 1 3 1 0 0 0 1 1 0 1

2 0 2 0 0 0 0 1 0 0 1 0

2 1 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

3 3 0 1 0 0 0 1 1 1 0 0

++++++++++++++++++++++++++

Zustand z3+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 1 1 3 1 0 0 0 0 1 0 1

0 3 3 3 1 0 0 0 1 1 1 1

1 3 1 3 1 0 0 0 1 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

z3+ <= (z0 and not x1 and x0) or (z0 and x1 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

Zustand z2+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 2 1 2 0 1 0 0 1 0 0 1

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0) or (z2 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

Zustand z1+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

1 2 0 1 0 0 1 0 1 0 0 0

2 1 1 1 0 0 1 0 0 1 0 1

2 3 3 1 0 0 1 0 1 1 1 1

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

Zustand z0+

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 0 0 0 0 0 1 1 0 0 0

2 0 2 0 0 0 0 1 0 0 1 0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 3 0 1 0 0 0 1 1 1 0 0

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or (z3 and not x1 and not x0) or (z3 and not x1 and x0) or (z3 and x1 and x0)

Ausgabe y1

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 2 2 0 1 0 0 0 0 1 0

0 3 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

2 0 2 0 0 0 0 1 0 0 1 0

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

Ausgabe y0

Zustand Eingabe Ausgabe Folgezustand Code Folgezustand Code Eingabe Code Ausgabe

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 1 0 1

0 2 3 3 1 0 0 0 1 1 1 1

1 0 3 2 0 1 0 0 0 0 1 1

1 1 3 2 0 1 0 0 0 1 1 1

1 2 1 3 1 0 0 0 1 1 0 1

2 0 1 1 0 0 1 0 0 1 0 1

2 2 1 2 0 1 0 0 1 0 0 1

2 3 3 1 0 0 1 0 1 1 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 1 1 0 0 0 0 1 0 1 0 1

3 2 1 3 1 0 0 0 1 0 0 1

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

z3+ <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0)

z2+ <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0)

z1+ <= (z1 and x1 and not x0) or (z2 and x0)

z0+ <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or not (z3 and x1 and not x0)

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0)

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) and (z3 and (x1 nand x0))

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121 is

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end;

architecture behaviour of derailleur_sn_20240121 is

begin

z3s <= (z0 and x0) or (z1 and x1 and x0) or (z3 and x1 and not x0);

z2s <= (z0 and not x1 and not x0) or (z1 and not x1) or (z2 and x1 and not x0);

z1s <= (z1 and x1 and not x0) or (z2 and x0);

z0s <= (z0 and x1 and not x0) or (z2 and not x1 and not x0) or (z3 and not x1 and not x0) or (z3 and not x1 and x0) or (z3 and x1 and x0);

y1 <= (z0 and not x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1) or (z2 and not (x1 xor x0)) or (z3 and not x1 and not x0);

y0 <= (z0 and x0) or (z1 and not (not x0 and x1)) or (z2 and (x1 or x0)) or (z3 and (x1 nand x0));

end;

library ieee;

use ieee.std_logic_1164.all;

entity derailleur_sn_20240121_testbench is

port (

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

z3s, z2s, z1s, z0s: inout std_logic;

y1, y0: inout std_logic

);

end;

architecture behaviour of derailleur_sn_20240121_testbench is

component derailleur_sn_20240121

port (

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

z3s, z2s, z1s, z0s: out std_logic;

y1, y0: out std_logic

);

end component;

begin

sn: derailleur_sn_20240121 PORT MAP (z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, y1=>y1, y0=>y0);

z0 <= '1' after 0 ns, '0' after 40 ns;

z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;

z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;

z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;

x0 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns;

x1 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns, '0' after 160 ns;

end;

Bzw. hier hat es keine Auswirkungen, weil es Eingangs und Ausgangsvariablen im Übergangsschaltnetz gäbe

zw, zw+