Nächste Seite: Neuer Automaten Generator Aufwärts: Graphen, Schaltwerke und Zahlen Vorherige Seite: Neue Übungen, unär Codierte

3 3 2 2

3 3 2 2

1 1 1 1

0 0 0 0

Zustand Eingabe Ausgabe Folgezustand

0 0 1 3

0 1 0 3

0 2 3 2

0 3 3 2

1 0 0 3

1 1 3 3

1 2 3 2

1 3 0 2

2 0 0 1

2 1 3 1

2 2 3 1

2 3 0 1

3 0 3 0

3 1 0 0

3 2 0 0

3 3 2 0

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 0 0 1

0 1 0 3 1 0 0 0 0 1 0 0

0 2 3 2 0 1 0 0 1 0 1 1

0 3 3 2 0 1 0 0 1 1 1 1

1 0 0 3 1 0 0 0 0 0 0 0

1 1 3 3 1 0 0 0 0 1 1 1

1 2 3 2 0 1 0 0 1 0 1 1

1 3 0 2 0 1 0 0 1 1 0 0

2 0 0 1 0 0 1 0 0 0 0 0

2 1 3 1 0 0 1 0 0 1 1 1

2 2 3 1 0 0 1 0 1 0 1 1

2 3 0 1 0 0 1 0 1 1 0 0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 0 0 0 0 0 1 0 1 0 0

3 2 0 0 0 0 0 1 1 0 0 0

3 3 2 0 0 0 0 1 1 1 1 0

+++++++++++++++++++++++++++++++++

z3+

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 0 0 1

0 1 0 3 1 0 0 0 0 1 0 0

1 0 0 3 1 0 0 0 0 0 0 0

1 1 3 3 1 0 0 0 0 1 1 1

z3+ <= (z0 and not x1 and not x0) or (z0 and not x1 and x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0)

z2+

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 3 2 0 1 0 0 1 0 1 1

0 3 3 2 0 1 0 0 1 1 1 1

1 2 3 2 0 1 0 0 1 0 1 1

1 3 0 2 0 1 0 0 1 1 0 0

z2+ <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and x1 and not x0) or (z1 and x1 and x0)

z1+

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

2 0 0 1 0 0 1 0 0 0 0 0

2 1 3 1 0 0 1 0 0 1 1 1

2 2 3 1 0 0 1 0 1 0 1 1

2 3 0 1 0 0 1 0 1 1 0 0

z1+ <= z2

z0+

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

3 0 3 0 0 0 0 1 0 0 1 1

3 1 0 0 0 0 0 1 0 1 0 0

3 2 0 0 0 0 0 1 1 0 0 0

3 3 2 0 0 0 0 1 1 1 1 0

z0+ <= z3

y1

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 2 3 2 0 1 0 0 1 0 1 1

0 3 3 2 0 1 0 0 1 1 1 1

1 1 3 3 1 0 0 0 0 1 1 1

1 2 3 2 0 1 0 0 1 0 1 1

2 1 3 1 0 0 1 0 0 1 1 1

2 2 3 1 0 0 1 0 1 0 1 1

3 0 3 0 0 0 0 1 0 0 1 1

3 3 2 0 0 0 0 1 1 1 1 0

y1 <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0) or (z3 and x1 and x0);

y0

Zustand Eingabe Ausgabe Folgezustand Folgezustand un"ar Eingabe bin"ar Ausgabe bin"ar

z3+ z2+ z1+ z0+ x1 x0 y1 y0

0 0 1 3 1 0 0 0 0 0 0 1

0 2 3 2 0 1 0 0 1 0 1 1

0 3 3 2 0 1 0 0 1 1 1 1

1 1 3 3 1 0 0 0 0 1 1 1

1 2 3 2 0 1 0 0 1 0 1 1

2 1 3 1 0 0 1 0 0 1 1 1

2 2 3 1 0 0 1 0 1 0 1 1

3 0 3 0 0 0 0 1 0 0 1 1

y0 <= (z0 and not x1 and not x0) or (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0);

z3+ <= (z0 and not x1 and not x0) or (z0 and not x1 and x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0);

z2+ <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and x1 and not x0) or (z1 and x1 and x0);

z1+ <= z2;

z0+ <= z3;

y1 <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0) or (z3 and x1 and x0);

y0 <= (z0 and not x1 and not x0) or (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0);

z3+ <= (z0 and not x1 and not x0) or (z0 and not x1 and x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0); z2+ <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and x1 and not x0) or (z1 and x1 and x0); z1+ <= z2; z0+ <= z3; y1 <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0) or (z3 and x1 and x0); y0 <= (z0 and not x1 and not x0) or (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0);

Trotz, des kleinen Fehlers, der nicht gravierend ist, weil er sich ändern lässt. Immerhin ist das nur ein Übungsprogramm aus ein paar Zeilen und selber nicht interessant. Das ist kein interessantes Programm an und für sich und lässt sich schnell ändern, ausserdem ist die Wahrscheinlichkeit gut, dass es richtigen Code erzeugt. Ich selber bin mehr an dem Schaltwerk interessiert

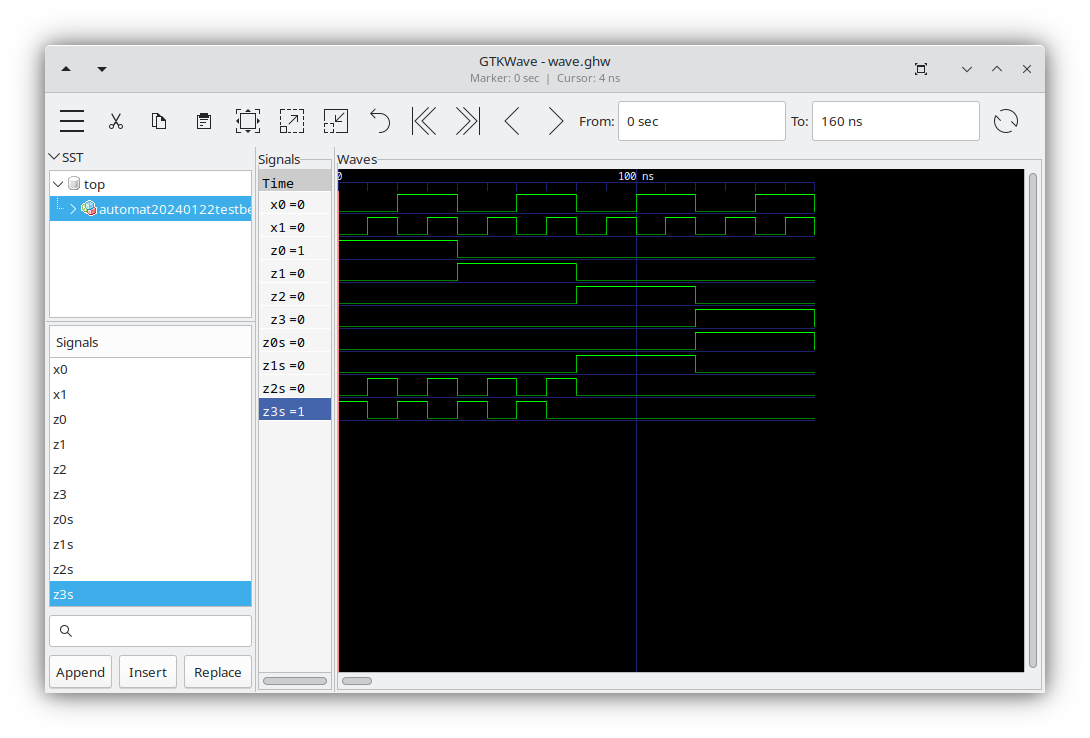

Hier der VHDL Code mit samt Ausgabe von GTKWAVE

library ieee;

use ieee.std_logic_1164.all;

entity automat20240122 is

port (

z3s, z2s, z1s, z0s: out std_logic;

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

y1, y0: out std_logic

);

end;

architecture behaviour of automat20240122 is

begin

z3s <= (z0 and not x1 and not x0) or (z0 and not x1 and x0) or (z1 and not x1 and not x0) or (z1 and not x1 and x0);

z2s <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and x1 and not x0) or (z1 and x1 and x0);

z1s <= z2;

z0s <= z3;

y1 <= (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0) or (z3 and x1 and x0);

y0 <= (z0 and not x1 and not x0) or (z0 and x1 and not x0) or (z0 and x1 and x0) or (z1 and not x1 and x0) or (z1 and x1 and not x0) or (z2 and not x1 and x0) or (z2 and x1 and not x0) or (z3 and not x1 and not x0);

end;

library ieee;

use ieee.std_logic_1164.all;

entity automat20240122testbench is

port (

z3s, z2s, z1s, z0s: inout std_logic;

z3, z2, z1, z0: inout std_logic;

x1, x0: inout std_logic;

y1, y0: inout std_logic

);

end;

architecture behaviour of automat20240122testbench is

component automat20240122

port (

z3s, z2s, z1s, z0s: out std_logic;

z3, z2, z1, z0: in std_logic;

x1, x0: in std_logic;

y1, y0: out std_logic

);

end component;

begin

sn: automat20240122 PORT MAP (z3s=>z3s, z2s=>z2s, z1s=>z1s, z0s=>z0s, z3=>z3, z2=>z2, z1=>z1, z0=>z0, x1=>x1, x0=>x0, y1=>y1, y0=>y0);

z0 <= '1' after 0 ns, '0' after 40 ns;

z1 <= '0' after 0 ns, '1' after 40 ns, '0' after 80 ns;

z2 <= '0' after 0 ns, '1' after 80 ns, '0' after 120 ns;

z3 <= '0' after 0 ns, '1' after 120 ns, '0' after 160 ns;

x1 <= '0' after 0 ns, '1' after 10 ns, '0' after 20 ns, '1' after 30 ns, '0' after 40 ns, '1' after 50 ns, '0' after 60 ns, '1' after 70 ns, '0' after 80 ns, '1' after 90 ns, '0' after 100 ns, '1' after 110 ns, '0' after 120 ns, '1' after 130 ns, '0' after 140 ns, '1' after 150 ns, '0' after 160 ns;

x0 <= '0' after 0 ns, '0' after 10 ns, '1' after 20 ns, '1' after 30 ns, '0' after 40 ns, '0' after 50 ns, '1' after 60 ns, '1' after 70 ns, '0' after 80 ns, '0' after 90 ns, '1' after 100 ns, '1' after 110 ns, '0' after 120 ns, '0' after 130 ns, '1' after 140 ns, '1' after 150 ns, '0' after 160 ns;

end;